逻辑综合概念

逻辑综合是根据时序/面积等约束, 将Verilog设计, 结合工艺库转换成门级网表的过程, 其中, 重点是时序约束.

Port和Pin的区别

通常来说, 一个Cell的引脚叫做Pin, 一个Design Block或者整个的SoC的IO叫做Pprt.

对于Cadence的EDA工具来说, Port被叫做I/O Pin.

寄存器的setup time与hold time

对于寄存器来说, 有两种类型的时序约束:

- setup time: 数据需要在时钟上升沿之前提前到来, 并且稳定一段时间, 稳定的这段时间叫做setup time.

- hold time: 数据需要在时钟上升沿到来之后稳定一段时间, 方便后边的模块进行采样, 稳定的这段时间叫做hold time.

- setup time约束电路的最大延时, hold time约束电路的最小延时.

- 时钟周期越小, setup time的要求越难以满足.

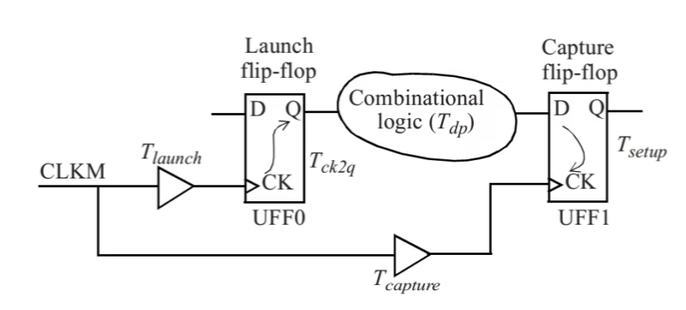

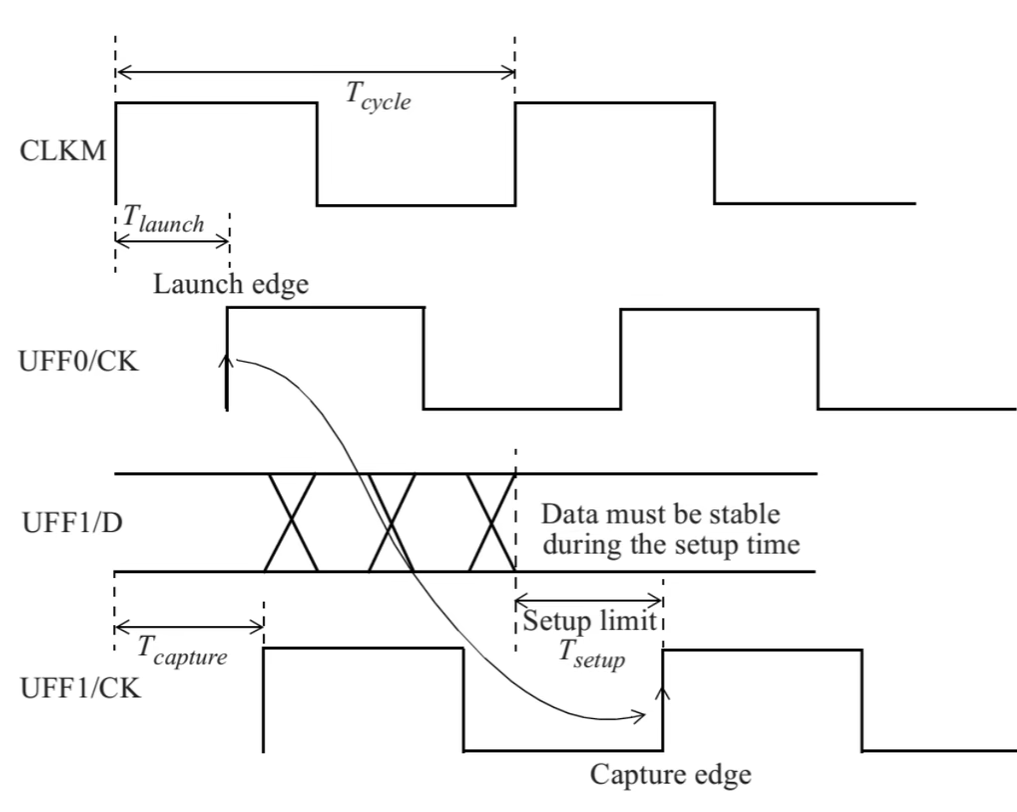

考虑如下模型:

几个变量的含义如下:

如果对第二个触发器满足setup time的要求, 需要有如下不等式成立:

不等式左边的一项叫做Data arrival time, 也就是数据到达第二个触发器D pin的时间.

不等式右边一项叫做Data require time, 就是setup time要求数据到达D pin的时间.

其中, Data require time与Data arrival time的差值叫做Slack, Slack大于等于0才能证明满足时序要求.

对于hold time, 需要有如下不等式成立:

其中, 右侧一项表示在$T_{capture} + T_{hold}$时刻之后, 数据才可以发生变化, 而前一项是data arrival time, 也就是说, 数据必须在前一个时钟上升沿到来, 然后再过一个hold time之后才能到.

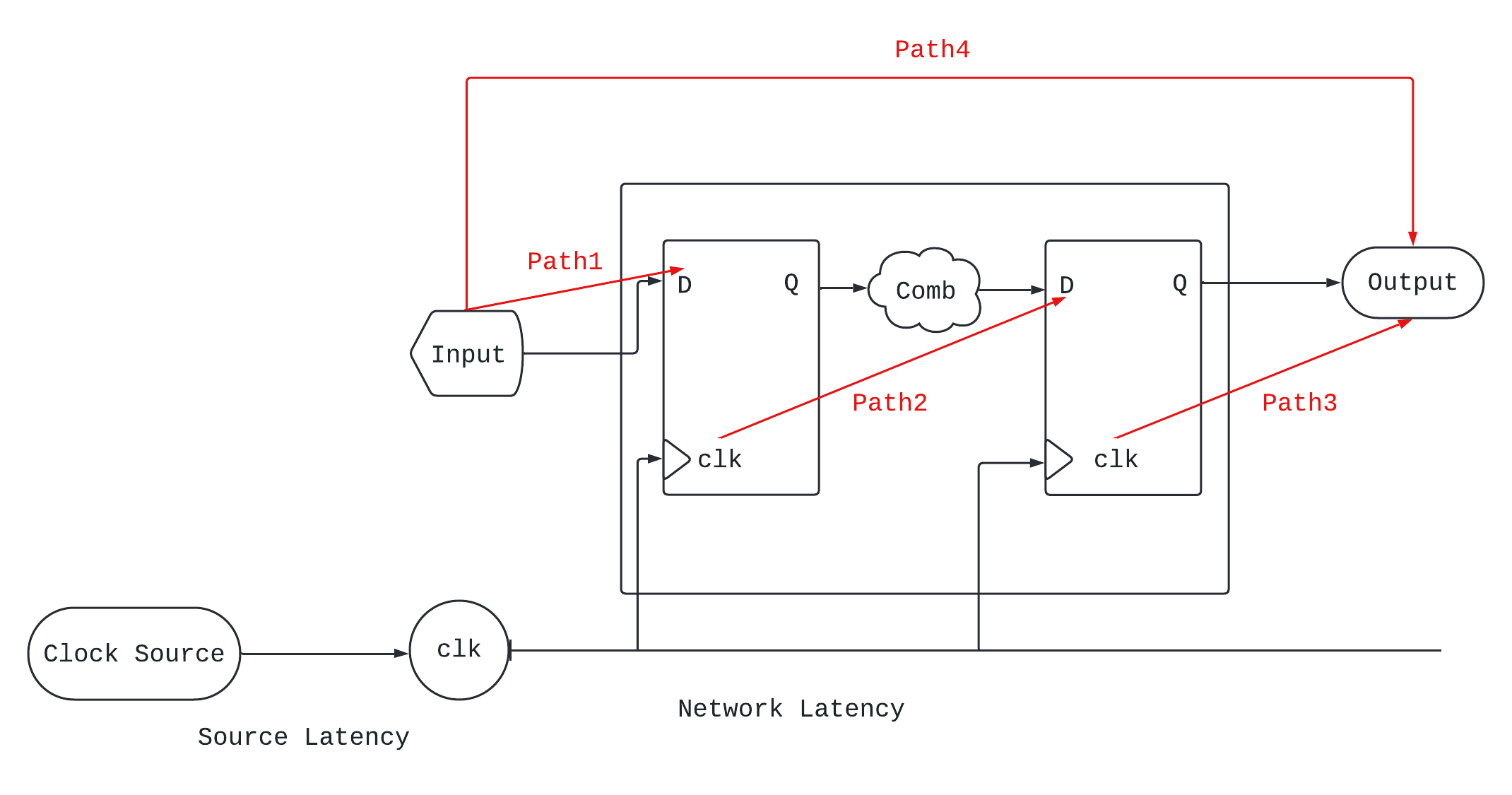

四种时序路径

考虑如下模型:

整个数字电路中的时序路径一共有四种:

- Input port到D pin的路径.

- Clk pin到D pin的路径, 对这条路径的约束本质上是约束时钟, 以及中间的组合逻辑.

- Clk pin到Output port的路径.

- Input port到Output port的路径, 对前三种路径进行约束之后, 第四种路径的约束就可以被覆盖.

对时钟的约束

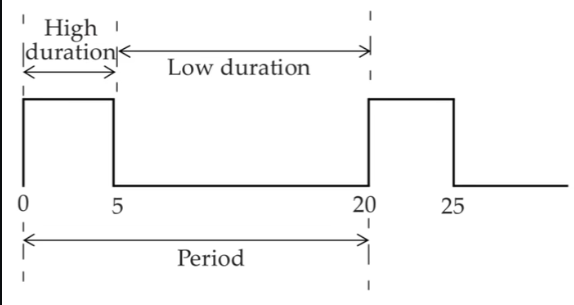

时钟周期和占空比

可以通过类似下面的命令指定时钟周期和占空比:

create_clock -name clk -period 20 -waveform {0 5} [get_ports clk]

- 其中,

-period指定时钟周期是20ns. -waveform制定时钟在一个时钟周期的0~5时刻处于高电平.

生成的时钟如下:

时钟误差

时钟误差(Clock Uncertainty)可以分为Clock Skew和Clock Jitter.

- Clock Skew: 从时钟树的根节点到某个Clock Pin之间会有延时.

- Clock Jitter: 时钟信号的上升沿会有前后抖动.

一般情况下可以用类似如下命令指定时钟误差:

set_clock_uncertainty $clk_uncertainty [all_clocks]

时钟延时

时钟延时(Clock Latency)可以分为Source Latency和Network Latency.

- Source Latency: 从时钟源到顶层模块的Clk Port的延时.

- Network Latency: 从时钟树的根节点到具体某个Clk pin的延时, 一般在时钟树综合之后才可以知道.

一般逻辑综合只会对Source Latency的最大值和最小值进行约束:

set clock_latency <value> -source -min [get_clocks CLK]

set clock_latency <value> -source -max [get_clocks CLK]

对I/O Port的约束

对I/O Port的约束本质上是对Input Port到D pin的时序路径和从Clk pin到Output Port的时序路径进行约束.

对于Input Port到D pin的路径, 可以设置Input Delay的最大值和最小值:

set_input_delay -clock <哪个时钟域> -max <max_value> [get ports INPUT_PORT]

set_input_delay -clock <哪个时钟域> -min <min_value> [get ports INPUT_PORT]

同样, 对于Clk pin到Output Port的路径, 可以设置Output Delay的最大值和最小值.

对组合逻辑的约束

在组合逻辑的路径中, 只有两种元素:

- 标准单元

- 线

这两种元素的延时有不同的计算方法, 但是这些计算方法都依赖标准工艺库(PDK)提供的数据.

环境约束

单元的延时估计必须在一定的条件下进行, 不同的条件对应不同的工艺库.

环境条件可以分为三种, 概括为PVT:

- 工艺: Process

- 电压: Voltage

- 温度: Temperature

其中:

- 电压高, 温度低, 延时越低.

- 电压低, 温度高, 延时越高.

厂商一般有三种工艺库:

- Slow process model: 延时最大, 检查setup time.

- Typical process model: 延时正常.

- Fast process model: 延时最小, 检查hold time.

线载模型(wireload model)

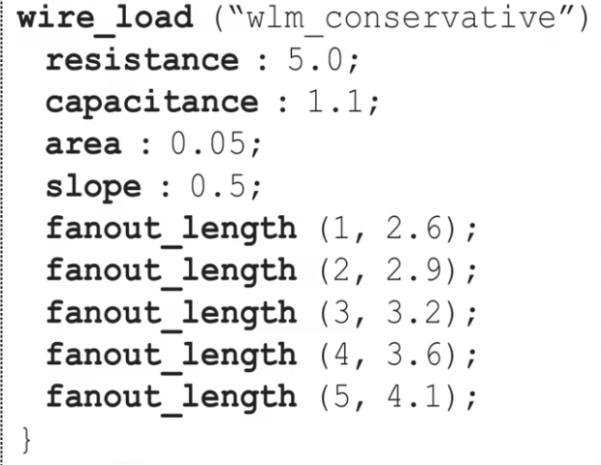

对于线载模型来说, fanout决定一切, 例如下面的这个线载模型的表格:

- 下面的

fanout_length规定了不同的fanout和线长的对应值, 通过fanout可以找到线长. - 上面的

resistance,capacitance,area和slope是一个系数, 用线长乘这个系数, 就可以得到真实值.

组合逻辑单元的延时模型

组合逻辑单元一般就是与, 或, 非门, 它们的延时取决于两个因素:

- Input transition time.

- Output load capacity

什么是Input transition time?

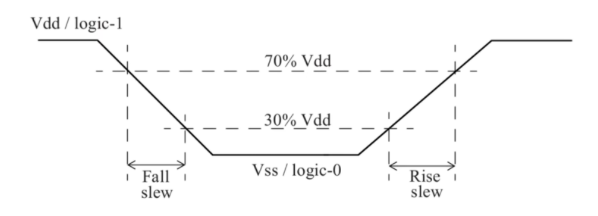

信号的电平一般不是垂直变化的, 实际情况下会像这样变化:

其中有两个threshold, 分别是70%和30%.

- 当电压高于70%时, 可以认为信号处于高电平.

- 当电压低于30%时, 可以认为信号处于低电平.

其中, input transition time对应从70%变化到30%这一段.

Input transition time和Output load capacity与标准单元延时的查找表可以从工艺库中找到.

可以使用类似如下命令设置Input transition time的最大最小值:

set_input_transition -max $ENV_data_input_max_transition $inputs

set_input_transition -min $ENV_input_min_transition $inputs

可以使用下面命令设置Output load capacity的最大/最小值:

set_load -max 0.050 [all_outputs]

set_load -max 0.004 [all_outputs]

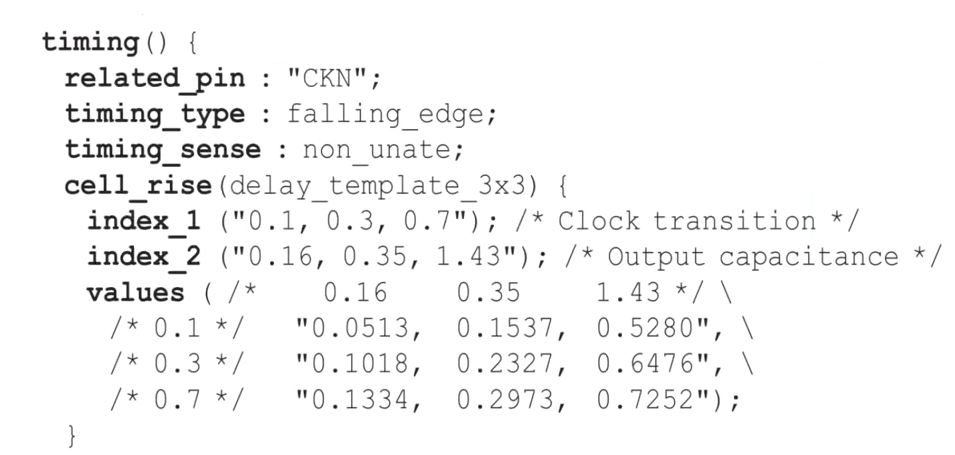

寄存器延时模型

setup time和hold time

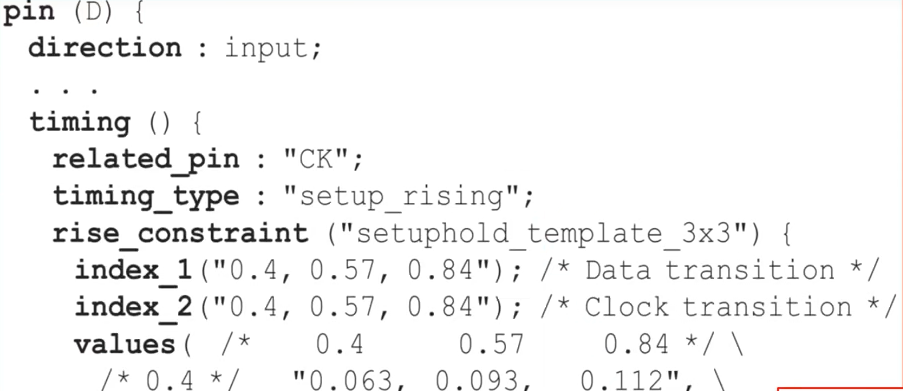

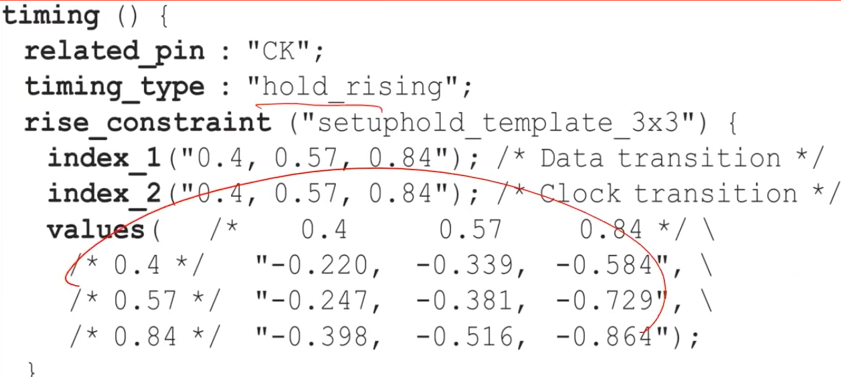

寄存器的setup time和hold time和Data transition time和Clock transition time有关, 可以在标准单元库中找到对应的查找表.

下面是setup time的查找表:

这个是hold time的查找表:

内部延时

内部延时主要是从Clk pin到Q pin的延时.

这种延时主要和Clock transition time与Q端的Output capacity有关, 也可以在标准单元库中查找到.

DRC检查

在综合时, 可以对某些Port设置一些Design Rule, 这些Design Rule可以包括:

- Max fanout

Max transition

…

命令类似这样:

set_max_fanout $DRC_max_fanout_inner [current_design];#40

set_max_fanout $DRC_max_fanout_input [all_inputs];#1

set_max_transition $DRC_data_max_transition [current_design]

set_max_transition $DRC_data_max_transition -data_path [all_clocks]

set_max_transition $DRC_clock_max_transition -clock_path [all_clocks]

综合完之后, 综合工具进行DRC检查, 来看综合后的电路是否满足这些要求.